集成電路(IC)測試儀是現代半導體產業中不可或缺的關鍵設備,其性能直接決定了芯片測試的精度、效率和可靠性。而電源電路作為測試儀的“能量心臟”,其穩定性、精度、噪聲水平和動態響應能力對測試結果的準確性具有決定性影響。因此,對集成電路測試儀電源電路進行深入的仿真設計研究,并推動其在實際應用中的優化,具有重要的理論價值和工程意義。

一、 研究背景與意義

隨著集成電路工藝節點不斷縮小,芯片功能日益復雜,對測試儀的要求也水漲船高。測試儀需要為被測器件(DUT)提供多種高精度、低噪聲的直流或動態電源,例如數字電源、模擬電源、參考電壓源等。任何電源的微小波動或噪聲都可能導致測試誤判,造成巨大的經濟損失。傳統的基于試驗板搭建和調試的設計方法周期長、成本高,且難以全面評估電源在極端工況下的性能。因此,采用先進的電路仿真技術,在設計階段對電源電路的拓撲結構、關鍵器件參數、環路穩定性、瞬態響應、熱性能及電磁兼容性(EMC)進行預測和優化,已成為提升測試儀電源設計質量與效率的必由之路。

二、 電源電路仿真設計的關鍵技術

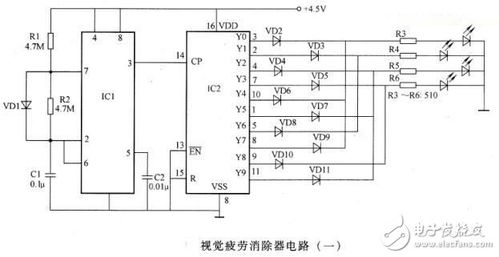

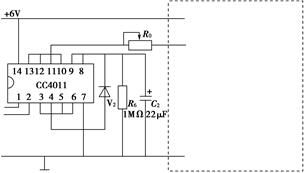

- 拓撲結構選擇與建模:根據測試儀的具體需求(如電壓范圍、電流能力、精度、紋波要求),選擇合適的電源拓撲,如低壓差線性穩壓器(LDO)、開關穩壓器(SMPS)或二者結合的混合方案。利用仿真軟件(如SPICE、SIMetrix/SPICE、PSpice)建立精確的器件模型和電路原理圖,是仿真成功的基礎。

- 直流與交流分析:通過直流分析確定靜態工作點;通過交流小信號分析,繪制環路增益與相位曲線,評估系統的穩定性(相位裕度與增益裕度),這是防止電路自激振蕩、確保動態性能的關鍵。

- 瞬態響應仿真:模擬負載階躍變化、輸入電壓波動等動態場景,分析電源的輸出電壓恢復時間、過沖/下沖幅度,以驗證其動態調整能力能否滿足高速測試的需求。

- 噪聲與紋波分析:特別針對測試儀中高精度模擬電路供電的LDO,需仿真其輸出噪聲頻譜和電源抑制比(PSRR)。對于開關電源,則需重點分析其開關紋波及高頻噪聲,并通過仿真優化濾波網絡。

- 熱分析與可靠性評估:利用電熱協同仿真,預測功率器件的結溫,評估散熱設計是否合理,確保電源在長期滿負荷工作下的可靠性。

- 電磁兼容性預仿真:對開關電源的布局布線進行寄生參數提取,仿真其傳導發射和輻射發射特性,從設計源頭抑制EMI問題。

三、 仿真設計在集成電路測試儀電源中的應用實踐

在實際項目中,仿真設計流程通常貫穿始終。在概念設計階段,通過系統級仿真確定電源架構和關鍵指標分配。在詳細設計階段,對每個電源模塊進行深入的電路級仿真,優化反饋網絡補償、選擇高性能的誤差放大器和功率器件。例如,為一個高精度引腳電子(PE)卡上的模擬電源設計LDO時,需要通過仿真精心調整運放的偏置、補償網絡和輸出級,以實現超低的噪聲(nV/√Hz級)和高達80dB以上的低頻PSRR。

在PCB布局布線前后,分別進行仿真對比尤為重要。前仿真基于理想布局,驗證電路原理的正確性;后仿真則導入PCB的寄生參數(如走線電阻、電感,過孔寄生電容),更真實地反映電源的實際性能,尤其是高頻響應和穩定性,從而指導布局的修改。

四、 挑戰與未來展望

盡管仿真技術極大地輔助了設計,但仍面臨挑戰。器件模型的準確性,特別是在高頻、高壓、大電流條件下的模型,直接影響仿真結果的可信度。多物理場(電-熱-應力)的復雜耦合仿真計算量巨大。隨著人工智能和機器學習技術的發展,有望實現仿真模型的自動校準、設計參數的智能優化以及故障模式的快速預測。將電源仿真與測試儀整體的數字仿真(如基于FPGA的時序控制)相結合,進行系統級協同仿真,將是實現更高性能、更智能化測試儀電源系統的趨勢。

結論

集成電路測試儀電源電路的仿真設計研究,是將先進設計方法學應用于高端測試裝備開發的具體體現。它通過虛擬原型技術,在硅前和板前階段最大限度地發現并解決問題,顯著縮短了開發周期,降低了研發成本,并從根本上提升了電源子系統乃至整機測試儀的穩定性和測試精度。隨著仿真工具與技術的不斷進步,其在推動集成電路測試技術向更高、更精、更可靠方向發展過程中,必將發揮越來越核心的作用。