在當(dāng)今的智能化浪潮中,機(jī)器視覺、嵌入式系統(tǒng)與集成電路(IC)設(shè)計(jì)構(gòu)成了現(xiàn)代電子系統(tǒng)的核心三角。它們協(xié)同工作,賦予設(shè)備“看”、“思考”和“行動(dòng)”的能力。本文將通過解析相關(guān)的典型電路設(shè)計(jì)圖,揭示這三者如何深度融合,并探討其設(shè)計(jì)精髓。

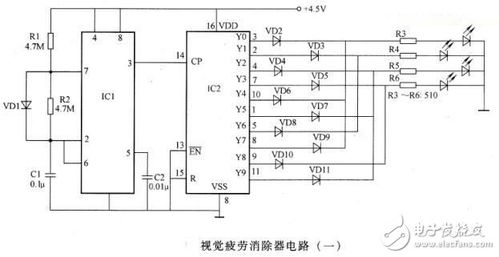

一、 機(jī)器視覺系統(tǒng)電路設(shè)計(jì)圖解析

機(jī)器視覺系統(tǒng)通常由圖像采集、處理與控制執(zhí)行三大部分構(gòu)成,其電路設(shè)計(jì)緊密圍繞這一流程展開。

- 圖像采集前端電路圖:這是系統(tǒng)的“眼睛”。典型設(shè)計(jì)圖會(huì)展示CMOS圖像傳感器(如OV系列)與主控芯片的連接。關(guān)鍵部分包括:

- 電源與時(shí)鐘電路:為傳感器提供穩(wěn)定、低噪聲的模擬電源(如2.8V AVDD)和精準(zhǔn)的像素時(shí)鐘(MCLK)。

- I2C/SPI配置接口電路:用于上電初始化傳感器,設(shè)置曝光時(shí)間、增益、輸出格式等參數(shù)。電路圖上會(huì)清晰標(biāo)注上拉電阻、走線長(zhǎng)度匹配等細(xì)節(jié)。

- 并行或MIPI CSI-2數(shù)據(jù)輸出接口:將原始圖像數(shù)據(jù)高速傳輸至處理器。這部分設(shè)計(jì)圖會(huì)強(qiáng)調(diào)數(shù)據(jù)線的等長(zhǎng)布線、差分對(duì)的阻抗控制,以及必要的ESD保護(hù)電路。

- 圖像處理核心電路圖:這是系統(tǒng)的“大腦”。在嵌入式領(lǐng)域,常用高性能ARM SoC(如NXP i.MX系列、TI Sitara系列)或專用視覺處理器(如Intel Movidius Myriad X)。設(shè)計(jì)圖重點(diǎn)包括:

- 核心電源樹(Power Tree)設(shè)計(jì):這類SoC通常需要多路(如1.0V內(nèi)核、1.8V DDR、3.3V IO)且時(shí)序嚴(yán)格的上電順序。電路圖會(huì)詳細(xì)展示PMIC(電源管理集成電路)的選型及其與SoC的配合。

- DDR內(nèi)存接口電路:用于緩存海量圖像數(shù)據(jù)。設(shè)計(jì)圖會(huì)精確布局DDR顆粒,遵循嚴(yán)格的拓?fù)浣Y(jié)構(gòu)(如Fly-by),并標(biāo)注終端匹配電阻(VTT),以確保信號(hào)完整性。

- 視頻輸入/輸出接口電路:如連接顯示器的HDMI/LVDS接口,或連接工業(yè)相機(jī)的GigE Vision接口。

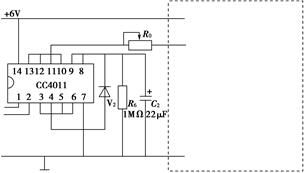

二、 嵌入式類電子電路設(shè)計(jì)圖集錦

嵌入式系統(tǒng)為機(jī)器視覺提供實(shí)時(shí)、可靠的運(yùn)行平臺(tái)。其電路設(shè)計(jì)強(qiáng)調(diào)穩(wěn)定性、低功耗和外圍接口的豐富性。

- 最小系統(tǒng)電路圖:任何嵌入式設(shè)計(jì)的基石。以STM32或ESP32為例,一張完整的最小系統(tǒng)圖必須包含:

- 復(fù)位電路:上電復(fù)位和手動(dòng)復(fù)位,通常采用RC電路。

- 時(shí)鐘電路:外部高速晶振(8-25MHz)和低速晶振(32.768kHz)的接法,包括負(fù)載電容的精確計(jì)算值。

- 啟動(dòng)模式配置電路:通過BOOT0/BOOT1引腳的電平設(shè)置,決定從Flash、系統(tǒng)存儲(chǔ)器還是RAM啟動(dòng)。

- 調(diào)試接口電路:SWD或JTAG接口的標(biāo)準(zhǔn)化連接,用于編程與調(diào)試。

- 功能擴(kuò)展電路圖:

- 通信接口:CAN總線、以太網(wǎng)(PHY芯片連接)、RS-485等工業(yè)通信接口的隔離電路設(shè)計(jì)(使用光耦或數(shù)字隔離器)。

- 運(yùn)動(dòng)控制接口:步進(jìn)電機(jī)/伺服驅(qū)動(dòng)器控制信號(hào)(PUL/DIR)的隔離與放大電路。

- 傳感器接口:模擬量輸入的ADC前端調(diào)理電路(運(yùn)放跟隨、濾波),以及數(shù)字溫濕度傳感器的單總線接口。

三、 集成電路(IC)設(shè)計(jì)在其中的角色與實(shí)現(xiàn)

上述的電路板級(jí)設(shè)計(jì),其核心效能最終取決于所使用的集成電路。IC設(shè)計(jì)本身則是在更微觀的層面進(jìn)行。

- 專用集成電路(ASIC)與現(xiàn)場(chǎng)可編程門陣列(FPGA):

- 對(duì)于高性能、低功耗的視覺處理任務(wù)(如卷積神經(jīng)網(wǎng)絡(luò)加速),常采用定制化ASIC(如谷歌TPU)或FPGA。相關(guān)的“電路圖”在這里表現(xiàn)為硬件描述語言(HDL)代碼(如Verilog/VHDL)綜合出的門級(jí)網(wǎng)表或FPGA底層布局布線圖。

- 設(shè)計(jì)圖集會(huì)展示如何用硬件邏輯單元構(gòu)建圖像流水線:從像素預(yù)處理(去馬賽克、伽馬校正)、到特征提取(Sobel邊緣檢測(cè)硬件模塊),再到結(jié)果輸出。

- 模擬混合信號(hào)IC設(shè)計(jì)圖:

- 圖像傳感器本身就是一個(gè)復(fù)雜的模擬混合信號(hào)IC。其設(shè)計(jì)版圖會(huì)展示像素陣列(光電二極管)、模擬前端(AFE)(包括放大器、相關(guān)雙采樣電路)、模數(shù)轉(zhuǎn)換器(ADC) 以及數(shù)字控制邏輯的物理布局。

- 電源管理IC(PMIC)的版圖則重點(diǎn)關(guān)注功率MOSFET的布局、反饋網(wǎng)絡(luò)的走線,以優(yōu)化效率和紋波。

四、 設(shè)計(jì)圖集錦的學(xué)習(xí)與應(yīng)用價(jià)值

一份優(yōu)秀的電路設(shè)計(jì)圖集錦,不僅僅是元件的連接手冊(cè),更是工程思想的載體。它傳遞了以下關(guān)鍵信息:

- 信號(hào)與電源完整性考量:展示了如何通過去耦電容布局、電源分割、參考平面設(shè)計(jì)來保證高速數(shù)字信號(hào)和敏感模擬信號(hào)的質(zhì)量。

- 電磁兼容性(EMC)設(shè)計(jì):揭示了濾波電路、屏蔽、接地策略的具體實(shí)現(xiàn)。

- 可制造性設(shè)計(jì)(DFM):體現(xiàn)了對(duì)封裝、焊盤、散熱、測(cè)試點(diǎn)的周全考慮。

- 模塊化設(shè)計(jì)思想:將復(fù)雜系統(tǒng)分解為圖像采集模塊、核心處理模塊、通信模塊等,便于復(fù)用和調(diào)試。

###

從宏觀的機(jī)器視覺系統(tǒng)板級(jí)原理圖,到嵌入式的核心控制板布局,再到微觀的集成電路晶體管級(jí)版圖,這三層設(shè)計(jì)環(huán)環(huán)相扣,共同構(gòu)建了智能設(shè)備的感知與決策基礎(chǔ)。研讀這些設(shè)計(jì)圖集錦,如同翻閱一部電子工程的立體教科書,不僅能指導(dǎo)具體的項(xiàng)目實(shí)施,更能深化對(duì)系統(tǒng)級(jí)、芯片級(jí)設(shè)計(jì)的整體理解,推動(dòng)我們?cè)O(shè)計(jì)出更高效、更智能的未來電子系統(tǒng)。