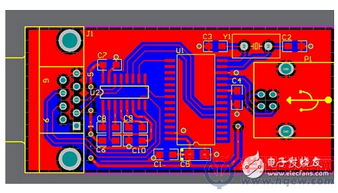

數字集成電路版圖設計是半導體芯片制造流程中的關鍵環節,它涉及將邏輯電路轉換為物理布局的過程。本部分將重點介紹使用Cadence IC工具進行原理圖繪制與仿真的基本流程。

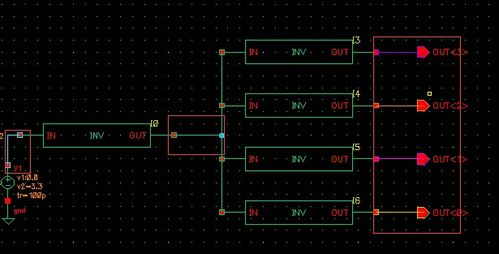

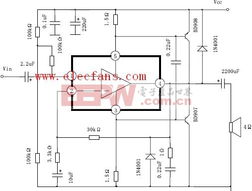

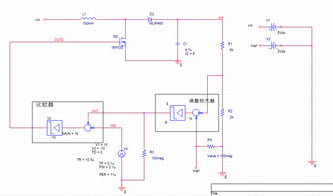

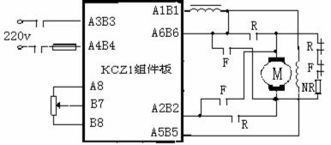

原理圖繪制是集成電路設計的基礎。在Cadence IC環境中,設計者通過圖形界面繪制電路圖,包括晶體管、電阻、電容等元件的連接。這一階段需要嚴格遵循設計規范,確保電路邏輯正確。工具提供了豐富的庫元件和連線功能,支持層次化設計,便于管理復雜電路。

仿真驗證是確保電路功能正確的關鍵步驟。Cadence IC集成了仿真工具如Spectre或Virtuoso,允許設計者對原理圖進行動態測試。通過輸入激勵信號,模擬電路在不同條件下的行為,包括時序、功耗和信號完整性分析。仿真結果可幫助識別設計錯誤,優化性能,減少后續物理實現的迭代次數。

原理圖繪制與仿真是版圖設計的前置工作,為后續布局布線提供可靠基礎。掌握這一流程,能有效提升集成電路設計的效率與準確性。