集成電路(Integrated Circuit, IC)設(shè)計是現(xiàn)代電子工業(yè)的核心,其過程復(fù)雜且精密,涉及從系統(tǒng)架構(gòu)到物理實現(xiàn)的多個層級。本文將通過圖文結(jié)合的方式,概述集成電路設(shè)計的關(guān)鍵環(huán)節(jié)與主流工具,并介紹如“熊貓辦公”這類資源平臺在設(shè)計過程中的輔助作用。

一、 集成電路設(shè)計流程全景圖

一套完整的集成電路設(shè)計流程,通常可以形象地通過一系列圖表來展示:

- 系統(tǒng)架構(gòu)與規(guī)格定義圖:此階段確定芯片的功能、性能、功耗和成本目標。示意圖通常展示頂層模塊劃分和總線互連結(jié)構(gòu)。

- 前端設(shè)計(邏輯設(shè)計)示意圖:

- RTL(寄存器傳輸級)代碼:以硬件描述語言(如Verilog/VHDL)編寫的源代碼,是設(shè)計的起點。圖示常為代碼片段與對應(yīng)電路模塊的映射關(guān)系。

- 功能仿真波形圖:展示信號在仿真環(huán)境下的時序變化,驗證邏輯正確性。圖中包含時鐘、復(fù)位及各數(shù)據(jù)信號的變化曲線。

- 綜合后網(wǎng)表結(jié)構(gòu)圖:將RTL代碼映射到標準單元庫后的邏輯門級連接圖,呈現(xiàn)為網(wǎng)狀拓撲結(jié)構(gòu)。

- 后端設(shè)計(物理設(shè)計)布局圖:

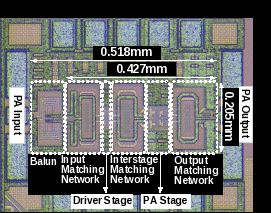

- 布局規(guī)劃(Floorplan)圖:定義芯片核心區(qū)域、模塊位置、I/O引腳和電源網(wǎng)絡(luò)的初步布局,形狀通常為矩形分區(qū)。

- 布局布線(Place & Route)效果圖:展示標準單元(邏輯門)的具體擺放位置以及單元之間多層金屬連線的走向,圖像色彩豐富,線條密集。

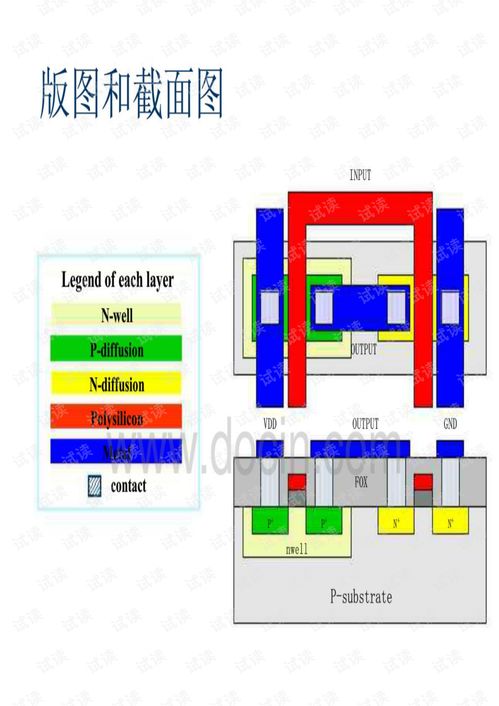

- 版圖(Layout)最終圖:設(shè)計完成的晶體管級幾何圖形,各層(如擴散層、多晶硅層、金屬層)用不同顏色和圖案區(qū)分,是交付制造的最終數(shù)據(jù)。

- 物理驗證圖:包括DRC(設(shè)計規(guī)則檢查)和LVS(版圖與電路圖一致性檢查)的報告示意圖,標示出可能存在的規(guī)則違反點。

- 驗證與測試相關(guān)圖表:

- 測試向量圖:用于芯片制造后測試的輸入輸出激勵模式圖。

- 封裝結(jié)構(gòu)圖:展示芯片裸片(Die)與封裝外殼(Package)的連接方式(如引線鍵合、倒裝焊)。

二、 主流設(shè)計工具與界面概覽

設(shè)計過程高度依賴EDA(電子設(shè)計自動化)工具,其用戶界面和生成的可視化報告是重要的“設(shè)計圖片”:

- 邏輯綜合工具(如Synopsys Design Compiler):界面顯示綜合約束、面積/時序報告以及優(yōu)化后的網(wǎng)表結(jié)構(gòu)視圖。

- 布局布線工具(如Cadence Innovus, Synopsys IC Compiler):提供交互式的芯片布局視圖,設(shè)計師可實時調(diào)整單元位置、查看布線擁塞熱力圖(通常用顏色深淺表示擁塞程度)。

- 版圖編輯與驗證工具(如Cadence Virtuoso, Mentor Calibre):核心界面是層次化的版圖編輯器,以及DRC/LVS驗證結(jié)果的圖形化標示。

- 電路仿真工具(如Cadence Spectre, Synopsys HSPICE):輸出詳細的瞬態(tài)、直流或交流分析波形圖。

三、 “熊貓辦公”等資源平臺的輔助角色

“熊貓辦公”這類綜合性辦公素材與模板平臺,雖然不提供專業(yè)的EDA工具,但能為集成電路設(shè)計的相關(guān)工作提供有益的素材支持:

- 設(shè)計文檔與演示制作:設(shè)計師在撰寫設(shè)計文檔、項目報告、技術(shù)方案或制作答辯PPT時,可以從平臺獲取:

- 專業(yè)的科技、電路主題PPT模板。

- 高質(zhì)量的電子元件、芯片、流程圖、數(shù)據(jù)圖表等矢量圖標與插圖。

- 統(tǒng)一的項目文檔格式模板,提升文檔規(guī)范性。

- 流程圖與架構(gòu)圖繪制:使用平臺提供的流程圖、組織結(jié)構(gòu)圖素材,可以快速繪制系統(tǒng)架構(gòu)圖、設(shè)計流程管理圖,使溝通更直觀。

- 團隊協(xié)作與知識管理:平臺可能提供的項目管理甘特圖模板、會議紀要模板等,有助于設(shè)計團隊進行進度管理和知識沉淀。

值得注意的是,核心的集成電路設(shè)計圖表(如版圖、仿真波形)必須由專業(yè)EDA工具生成以確保其準確性和可制造性。而“熊貓辦公”等平臺提供的素材,主要用于外圍的表達、溝通和文檔美化工作。

集成電路設(shè)計的“圖片大全”,實質(zhì)上是其復(fù)雜設(shè)計流程與技術(shù)內(nèi)涵的可視化體現(xiàn)。從抽象的代碼到具體的幾何圖形,每一張圖表都是設(shè)計思想與工程智慧的結(jié)晶。理解這些圖表,有助于把握芯片設(shè)計的精髓。善于利用“熊貓辦公”等資源平臺來提升設(shè)計文檔的呈現(xiàn)效果與團隊協(xié)作效率,也是現(xiàn)代IC設(shè)計師一項有價值的輔助技能。