電磁兼容性(EMC)浪涌保護(hù)電路在現(xiàn)代集成電路(IC)設(shè)計(jì)中至關(guān)重要,旨在防止瞬態(tài)電壓事件(如雷擊、開(kāi)關(guān)操作)對(duì)電子設(shè)備造成損害。本文將從原理和設(shè)計(jì)兩方面,探討集成電路中的EMC浪涌保護(hù)電路。

一、EMC浪涌保護(hù)電路的基本原理

EMC浪涌保護(hù)電路的核心是響應(yīng)瞬態(tài)過(guò)電壓,將其能量導(dǎo)向安全路徑,避免損壞敏感IC組件。浪涌通常指持續(xù)時(shí)間短(微秒至毫秒)、電壓高(可達(dá)數(shù)千伏)的脈沖。在集成電路中,保護(hù)機(jī)制基于半導(dǎo)體器件的快速開(kāi)關(guān)特性,常見(jiàn)原理包括:

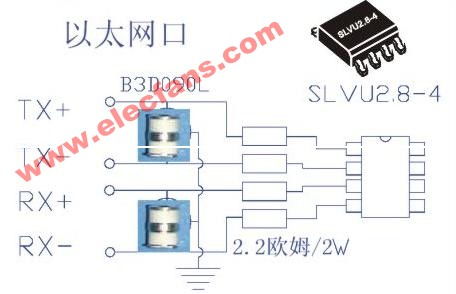

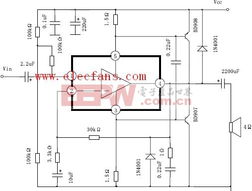

1. 鉗位原理:使用齊納二極管或瞬態(tài)電壓抑制器(TVS)將電壓限制在安全水平。當(dāng)浪涌電壓超過(guò)閾值時(shí),器件迅速導(dǎo)通,形成低阻抗路徑,分流電流。

2. 能量吸收原理:通過(guò)電阻、電容或?qū)S媒Y(jié)構(gòu)(如硅控整流器SCR)耗散浪涌能量,轉(zhuǎn)化為熱能。

3. 隔離原理:利用電感或變壓器隔離高頻浪涌,防止其傳播到IC核心部分。

這些原理在IC設(shè)計(jì)中需結(jié)合工藝特性,例如利用CMOS工藝的寄生二極管或晶體管實(shí)現(xiàn)集成保護(hù)。

二、EMC浪涌保護(hù)電路的設(shè)計(jì)方法

在集成電路設(shè)計(jì)中,EMC浪涌保護(hù)需從系統(tǒng)級(jí)和器件級(jí)綜合考慮,確保高性能、小面積和低成本。設(shè)計(jì)步驟如下:

- 需求分析:確定浪涌標(biāo)準(zhǔn)(如IEC 61000-4-5),包括電壓峰值、波形(如8/20μs)和耐受等級(jí)。根據(jù)IC應(yīng)用場(chǎng)景(如汽車(chē)、工業(yè))設(shè)定保護(hù)目標(biāo)。

- 拓?fù)溥x擇:常見(jiàn)拓?fù)浒ǎ?/li>

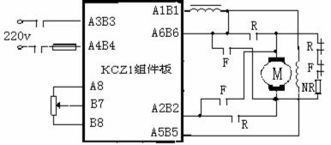

- 輸入/輸出(I/O)保護(hù):在引腳處集成TVS或二極管鉗位電路,防止靜電放電(ESD)和浪涌。

- 電源保護(hù):使用去耦電容和電壓調(diào)節(jié)器,結(jié)合片上TVS,吸收電源線上的瞬態(tài)能量。

- 多級(jí)保護(hù):串聯(lián)電阻、電感和TVS,實(shí)現(xiàn)分級(jí)能量耗散,提高可靠性。

- 器件設(shè)計(jì):利用IC工藝設(shè)計(jì)保護(hù)器件:

- TVS二極管:優(yōu)化摻雜剖面和結(jié)面積,以實(shí)現(xiàn)低鉗位電壓和高能量處理能力。

- MOS基保護(hù):設(shè)計(jì)柵極耦合或襯底觸發(fā)結(jié)構(gòu),實(shí)現(xiàn)快速響應(yīng)。

- 寄生元件利用:合理布局以減少寄生電感和電阻,避免性能下降。

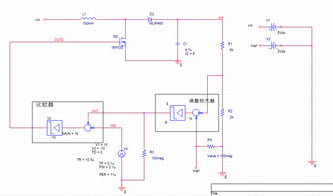

- 仿真與驗(yàn)證:使用SPICE或?qū)S肊DA工具進(jìn)行瞬態(tài)仿真,檢查鉗位電壓、響應(yīng)時(shí)間和熱效應(yīng)。通過(guò)實(shí)驗(yàn)測(cè)試(如浪涌發(fā)生器)驗(yàn)證設(shè)計(jì),確保符合EMC標(biāo)準(zhǔn)。

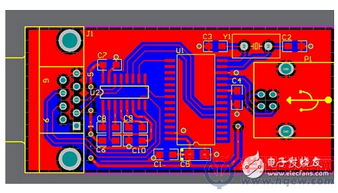

- 布局優(yōu)化:在IC版圖中,將保護(hù)電路靠近I/O焊盤(pán),減少寄生效應(yīng);采用對(duì)稱(chēng)布局以均衡電流分布,避免局部過(guò)熱。

三、設(shè)計(jì)挑戰(zhàn)與未來(lái)趨勢(shì)

IC中的EMC浪涌保護(hù)面臨尺寸縮小、高頻應(yīng)用等挑戰(zhàn)。例如,先進(jìn)節(jié)點(diǎn)下,器件更易受浪涌損傷,需開(kāi)發(fā)新型材料(如寬禁帶半導(dǎo)體)。未來(lái)趨勢(shì)包括智能保護(hù)電路(集成傳感器和控制器)、系統(tǒng)級(jí)封裝(SiP)集成外部保護(hù)元件,以及AI輔助設(shè)計(jì)優(yōu)化。

EMC浪涌保護(hù)電路是集成電路可靠性的關(guān)鍵。通過(guò)深入理解原理并采用系統(tǒng)化設(shè)計(jì)方法,工程師可以有效提升IC的抗浪涌能力,滿(mǎn)足日益嚴(yán)格的EMC要求。