在電子競賽或教學活動中,搶答器是一種常見的設備,用于快速判斷參與者的響應順序。本文詳細介紹基于74LS171集成電路的四路搶答器設計,包括器件選型、電路原理、工作過程以及實現功能。

一、設計背景與目標

搶答器廣泛應用于知識競賽、課堂互動等場景,要求能夠準確記錄最先按下按鈕的參與者,并鎖定顯示結果,避免后續操作干擾。本設計采用74LS171四D觸發器集成電路為核心,構建一個穩定、成本低且易于實現的四路搶答器。

二、核心器件介紹

74LS171是TTL邏輯系列的集成電路,包含四個獨立的D觸發器,具有公共時鐘和清除功能。其引腳包括數據輸入(D0-D3)、時鐘輸入(CLK)、清除輸入(CLR)以及輸出(Q0-Q3)。在搶答器中,74LS171用于存儲和鎖定第一個搶答信號。

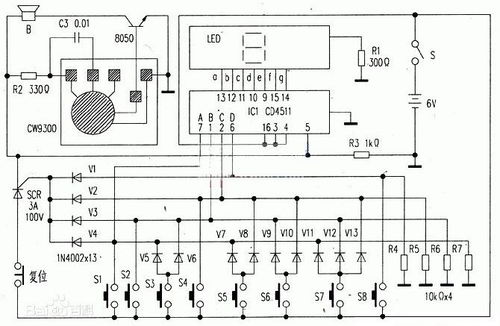

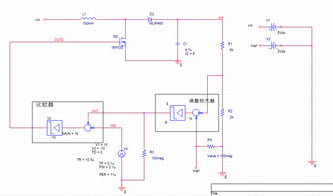

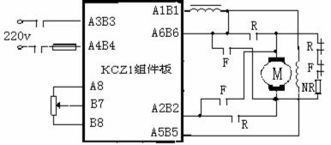

三、電路設計原理

- 輸入部分:四路搶答按鈕(S1-S4)分別連接到74LS171的數據輸入引腳(D0-D3)。按鈕常態為斷開狀態,輸入低電平;按下時提供高電平信號。

- 時鐘控制:所有觸發器的時鐘引腳(CLK)連接在一起,通過一個公共的時鐘信號控制。通常,時鐘由按鈕動作觸發,例如使用一個或門組合搶答按鈕信號,生成時鐘脈沖。

- 清除功能:清除引腳(CLR)連接到一個總清除按鈕,當按下時,將所有觸發器復位,輸出低電平,準備下一輪搶答。

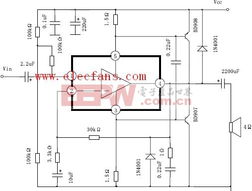

- 輸出與顯示:輸出引腳(Q0-Q3)連接到LED指示燈或數碼管解碼電路,用于顯示搶答結果。例如,當某一路搶答成功時,對應輸出高電平,點亮LED。

- 鎖定機制:通過74LS171的邊沿觸發特性,第一個時鐘上升沿鎖存數據,確保后續按鈕操作無效,直到清除信號復位。

四、工作過程詳解

- 初始狀態:清除信號有效,所有輸出為低電平,指示燈熄滅。

- 搶答階段:參與者按下按鈕時,對應數據輸入變為高電平。第一個按鈕按下產生時鐘上升沿,74LS171鎖存該路數據,輸出高電平并保持,同時指示燈亮起。

- 鎖定與顯示:一旦某一路被鎖定,其他按鈕按下不會改變輸出,直到主持人按下清除按鈕,系統復位。

五、優點與改進建議

本設計基于74LS171,具有結構簡單、響應快、成本低的優點。TTL邏輯可能受噪聲影響,建議添加去抖動電路(如RC濾波器或專用去抖動IC)以提高穩定性。可擴展為更多路搶答器,通過級聯74LS171或其他邏輯器件實現。

六、總結

通過74LS171集成電路,四路搶答器設計實現了基本的搶答功能,突出了數字電路在現實應用中的實用性。該設計適合電子初學者學習和實踐,可根據需求進一步優化,如添加聲音提示或數字顯示功能。掌握此類電路設計有助于深入理解時序邏輯和集成電路的應用。