專用集成電路(ASIC)是現代電子系統的核心組件,其設計涉及多個關鍵技術領域,其中CMOS組合邏輯設計是基礎且至關重要的環節。本文將系統介紹CMOS組合邏輯設計的基本原理、設計流程及其在集成電路中的應用。

一、CMOS組合邏輯的基本原理

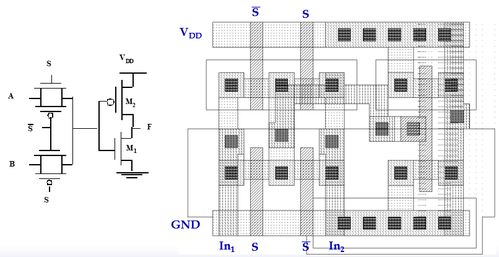

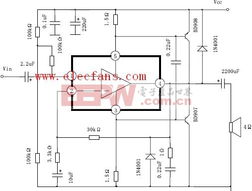

CMOS(互補金屬氧化物半導體)技術因其低功耗和高集成度優勢,成為當前集成電路設計的主流。組合邏輯電路的特點是輸出僅取決于當前輸入信號,無記憶功能。在CMOS設計中,通過NMOS和PMOS晶體管的互補組合實現邏輯功能:NMOS管用于下拉網絡(傳遞邏輯0),PMOS管用于上拉網絡(傳遞邏輯1)。例如,基本的CMOS反相器由一個PMOS和一個NMOS管構成,當輸入為高電平時NMOS導通輸出低電平,輸入低電平時PMOS導通輸出高電平。

二、CMOS組合邏輯的設計流程

- 邏輯功能定義:根據系統需求確定真值表或邏輯表達式。

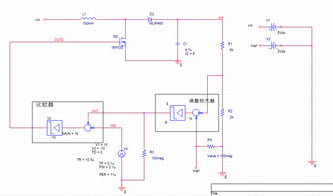

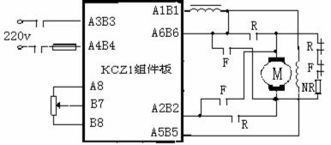

- 電路結構設計:將邏輯表達式轉化為CMOS實現結構,常用方法包括靜態CMOS、傳輸門邏輯等。靜態CMOS通過上拉網絡(PMOS)實現邏輯函數的“非”形式,下拉網絡(NMOS)實現原函數。

- 晶體管尺寸優化:根據速度、功耗和面積要求確定晶體管寬長比,通常需要平衡上升時間和下降時間。

- 仿真驗證:使用SPICE等工具進行時序、功耗和功能仿真。

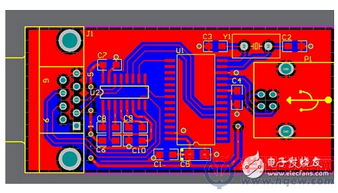

- 版圖設計:按照設計規則繪制物理布局,考慮寄生參數和工藝變異影響。

三、設計關鍵考量因素

- 功耗控制:CMOS電路的靜態功耗極低,但動態功耗與開關頻率和負載電容成正比,需通過時鐘門控和邏輯優化降低功耗。

- 速度優化:關鍵路徑延遲受晶體管開關速度和互連線RC延遲影響,可通過晶體管尺寸調整和邏輯重構改善。

- 噪聲容限:確保電路在電源電壓波動和噪聲干擾下仍能可靠工作。

- 可測試性:在設計階段需考慮故障模型和測試策略,如掃描鏈插入。

四、在集成電路中的應用與發展

CMOS組合邏輯廣泛用于各類ASIC中,包括算術邏輯單元(ALU)、多路選擇器、編碼器等模塊。隨著工藝進步至納米級別,新型器件如FinFET的應用和低功耗設計技術如電源門控的引入,正在推動CMOS組合邏輯向更高性能、更低功耗方向發展。基于CMOS的可編程邏輯結構(如FPGA中的可配置邏輯塊)也擴展了組合邏輯的實現靈活性。

CMOS組合邏輯設計是集成電路設計的基石,設計師需要深入理解器件特性與系統需求,通過精心優化實現性能、功耗和成本的平衡。隨著異構集成和智能設計工具的發展,CMOS組合邏輯將繼續在人工智能、物聯網等新興領域發揮關鍵作用。